Speaking to partners last week as part of their annual Open Innovation Platform forum in Europe, a big portion of TSMC’s roadshow was dedicated to the next generation of the company’s foundry technology. TSMC’s 2 nm-class N2, N2P, and N2X process technologies are set to introduce multiple innovations, including nanosheet gate-all-around (GAA) transistors, backside power delivery, and super-high-performance metal-insulator-metal (SHPMIM) capacitor over the next few years. But in order to take advantage of these innovations, TSMC warns, chip designers will need to use all-new electronic design automation (EDA), simulation, and verification tools as well as IP. And while making such a big shift is never an easy task, TSMC is bringing some good news to chip designers early-on: even with N2 still a couple of years out, many of the major EDA tools, verification tools, foundation IP, and even analog IP for N2 are already available for use.

“For N2 we could be working with them two years in advance already because nanosheet is different,” said Dan Kochpatcharin, Head of Design Infrastructure Management at TSMC, at the OIP 2023 conference in Amsterdam. “[EDA] tools have to be ready, so what the OIP did is to work with them early. We have a huge engineering team to work with the EDA partners, IP partners, [and other] partners.”

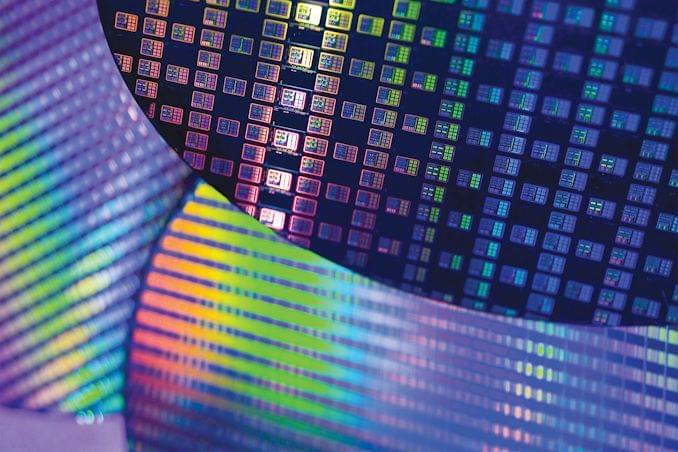

*Chip density published by TSMC reflects ‘mixed’ chip density consisting of 50% logic, 30% SRAM, and 20% analog.